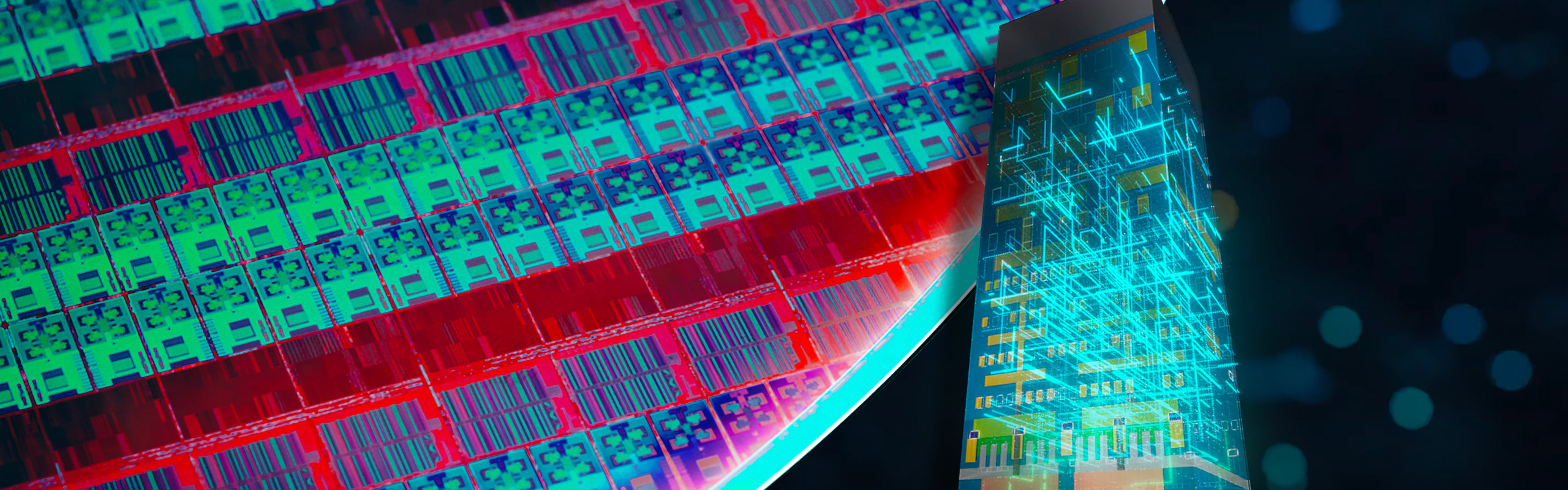

Tweakers woonden een technische briefing bij waarin Intel zijn PowerVia-ontwikkelingen vooraf aan VLSI deelden met de media. In dit artikel bespreken we de werking van backside power delivery, wat de voordelen zijn en waarom het verplaatsen van de chipstroomvoorziening misschien lastiger is dan je zou denken.

Wat is vermogensafgifte aan de achterkant?

Traditioneel gezien bestaat een chip uit een enorm aantal transistors, met daarboven diverse metaallagen. In de metaallagen zitten twee verschillende netwerken met interconnects: een voor de stroomvoorziening en een voor signaalverwerking. Naarmate transistors kleiner worden, moeten die netwerken meekrimpen.

Die netwerken die elkaar aan elkaar koppelen, zorgen steeds meer op de weg, wat de lagere transistors bemoeilijkt. Daarnaast creëren de verschillende lagen interferentie. Door een hogere weerstand aan de voorkant kan de spanning van de toegevoerde stroom afnemen, een fenomeen dat ook wel IR-droop heet. Dat zijn allemaal ongewenste effecten.

Backside power delivery moet op deze gebieden verlichting bieden door het stroomvoorzieningsnetwerk te verplaatsen. Bij backside power delivery wordt de voorkant van de wafer dus volledig gereserveerd voor de signaalverwerking. De verbindingen voor stroomvoorziening, die volgens Intel tot twintig procent van de wafervoorkant kunnen innemen, worden op hun beurt allemaal naar de achterkant verwerkt. Beide netwerken zijn losgekoppeld, elkaar niet langer in de weg zitten en afzonderlijk kunnen worden afgebroken.

Er zijn verschillende manieren om backside power delivery te implementeren. Ze verschillen op het gebied van afnemende en ruimtebesparing, zoals begraven stroomrails en nano-tsv’s. Intel kiest voor zijn PowerVia-techniek voor de tweede optie: kleine door-silicium via-verbindingen die door de wafer lopen en direct in verbinding staan met de transistor.

Het verschil tussen die twee implementaties wordt bewezen in de onderstaande slide. Begraven stroomrails zijn bedoeld om te implementeren. Soortgelijke powerrails worden gebruikt zonder stroomafgifte aan de achterkant. Het nadeel van deze optie is dat de stroomvoorziening, ook met stroomafgifte aan de achterkant, nog steeds delen van bovenaf moeten komen, zoals Intel in zijn presentatie aantoont met een gele pijl. Chipmakers moeten daarom ruimte voor stroomverbindingen vrijmaken in de toekomstige M0-laag, die direct boven op de transistors zit. Met nano-tsv’s is dat niet het geval; die staan vanaf de zijkant in verbinding met de transistor. betrokkenheid wordt ook de M0-laag volledig aan signaalnetwerken bevestigd.

Testnodes en PowerVia-chips: Blue Sky Creek

Intel zal PowerVia toevoegen aan zijn 20A-procedure, waarop massaproductie in de eerste helft van vorig jaar van start gaat. Behalve op de achterkant van de stroomvoorziening stapt het bedrijf bij die node ook over op een geheel nieuwe transistorarchitectuur: RibbonFET.

Om te voorkomen dat de introductie van twee nieuwe, complexe technieken tot productieproblemen leidt, heeft Intel een interne procedure ontwikkeld om PowerVia productieklaar te krijgen. Het knooppunt is nog steeds gebaseerd op de traditionele finfets die chipproducenten al ruim een decennium gebruiken. Het idee daarachter is dat bedrijf op de manier waarop PowerVia kan ontwikkelen, nadat deze beëindiging gebruikt kan worden om de techniek vrijwel gemakkelijk te implementeren in combinatie met RibbonFET-transistoren.

:strip_exif()/i/2005818320.jpeg?f=imagenormal)

Op deze manier wil de fabrikant niet veel hooi op zijn vork nemen met verschillende technische veranderingen in één knooppunt. Dat moet een situatie als door Intels 10nm-procedure voorkomen. Die node werd door yieldproblemen jaren te laat opgeleverd, waardoor het bedrijf zes jaar lang processors op 14nm moest uitbrengen. Ceo Pat Gelsinger reflecteerde jaren later op vragen van Tweakers dat Intel met 10nm te veel gelijktijdig wilde doorvoeren en daardoor in de problemen kwam.

Bron: Intel, VLSI

Intel baseert zijn PowerVia-testprocedure op Intel 4, dat voorheen bekendstond als 7nm. begeleidende het bedrijf onlangs een eerste testchip, genaamd Blue Sky Creek. Deze chip is gebaseerd op Intels eerste Meteor Lake-processors, de chipfabrikant zal later dit jaar bijdragen aan laptops. Blue Sky Creek gebruikte daarvoor nieuwe Crestmont-kernen.

Intel koos voor deze op diepte gerichte E-cores omdat ze al ontwikkeld waren op basis van de Intel 4-procedure. Daarom konden ze gemakkelijk worden overgeheveld naar de PowerVia-testnode. Daarnaast zijn E-kernen compact. daardoor zijn grote test-overlijdt, inclusief de yielduitdagingen die bij het komen kijken, niet nodig. De cores halen volgens de handleiding een kloksnelheid van 3GHz op 1,1V.

Hoe zo’n chip er van binnen uitziet, is te zien op de onderstaande dia. Aan de bovenkant zijn de verschillende signaalverbindingen te zien, onder de noemer FS Metals. Onderaan, aangegeven als ‘BS PDN’, staan de verbindingen voor de stroomvoorziening aan de achterkant. In het midden staan weer verticale witte strepen, die met een gele lijn zijn gemarkeerd; dat zijn de eerder besproken nano-tsv’s die de transistors verbinden met het stroomvoorzieningsnetwerk aan de onderkant.

PowerVia in de praktijk: wat zijn de voordelen?

We hebben het belangrijkste voordeel van PowerVia, eigenlijk ook wel genoemd: de ruimtebesparing aan de voorkant die verdere transistorverkleiningen iets gemakkelijker moet maken. Daardoor kon het bedrijf onder meer de toonhoogte in zijn M0-laag verhogen van 30 naar 36nm. Die pitch staat voor de afstand tussen de verschillende interconnectlijntjes; een hogere toonhoogte betekent een grotere afstand en daarmee een goedkopere productie.

Volgens Intel compenseert de kostenbesparing met zijn hogere pitch de extra kosten voor backside power delivery ruimschoots, zeker bij toekomstige knooppunten. De overige afmetingen zijn verdwenen, zoals de afstand tussen vinvormige kanalen en de gecontacteerd polypitchdie de afstand tussen gates dicteert: vertrouwd 30 en 50nm.

Door die wijzigingen, samen met het verlagen van de hoeveelheid wijn van drie naar twee, wist Intel de ‘hoogte’ van een standaardcel te verlagen van 240 naar 210nm. Zo’n standaardcel omvat een groep transistors die een logische of opslagfunctie kunnen uitvoeren. Dat betekent dat het celformaat overeenkomt met 12,5 procent tien overeenkomsten van Intel 4 zonder PowerVia.

:strip_exif()/i/2005818630.jpeg?f=imagenormal)

De testprocedure van Intel wist zeker beter gebruik te maken van de beschikbare ruimte binnen standaardcellen. Op delen van de dood gaan wist de fabrikant naar eigen zeggen een standaardcel-gebruik van ‘meer dan 90 procent’ te behalen. Het bedrijf zegt niet wat de celdichtheid is zonder PowerVia, hoewel dat percentage in ieder geval lager ligt. Die verbetering is daarmee deels afkomstig uit PowerVia, hoewel het gebruik van euv-lithografie in Intel 4 zeker ook een bijdrage zal hebben geleverd.

Los van de chipproductievoordelen, moet de uitkomst zelf ook baat hebben bij PowerVia. Intel noemt in zijn slides een ‘prestatieverbetering’ van zes procent op zijn Blue Sky Creek-chip. Tijdens een vragensessie met journalisten verduidelijkte de fabrikant dat de maximale kloksnelheden zes procent hoger liggen. Die voortgang werd volgens Intel puur verbruik door het verbruik van PowerVia, zonder verdere wijzigingen aan de kern. De IR Drop, de afname van de spanning voordat deze de transistor bereikte, ruim dertig procent.

Illustratie met de celdichtheid (links) en de conclusie op het gebied van IR-droop en frequentietoename. Bron: Intel

Obstakels: opbrengst, hit en debugging

Los van de voordelen brengt PowerVia ook enkele risico’s met zich mee. Intel noemt tijdens zijn briefing drie voorbeelden: opbrengsten, temperaturen en debugging. Eerstgenoemde heeft te maken met de defecten die tijdens het chipproductieproces kunnen ontstaan. Bij de implementatie van PowerVia draait Intel een wafer om, waarschijnlijk wordt al het silicium weggepolijst totdat de onderkant van de transistors zichtbaar is. Daarbovenop worden vervolgens de metaallagen met nano-tsv’s en de mogelijke stroominterconnects genomen. Tijdens dat proces kunnen, net als bij andere chipproductiestappen, natuurlijk defecten optreden.

Intel zegt zelf dat zijn PowerVia-testnode momenteel alle opbrengsten haalt die geschikt zijn voor massaproductie. Het testproces gaat over dat gebied ongeveer twee kwartalen achter op zijn ‘gewone’ Intel 4-node, die al in massaproductie is. Het bedrijf noteerde een gevolg geen stroom gerelateerde betrouwbaarheidsproblemen bij de overstap naar PowerVia. De verwachting is daarmee dat PowerVia volgend jaar relatief probleemloos overgeheveld kan worden naar 20A.

Warmte werd ook gezien als een potentieel obstakel. Waar transistors voorheen op het uiteinde van de wafel zaten, zijn ze met PowerVia midden in de wafel ingekapseld tussen twee lagen. Dat kan de koeling van de transistors bemoeilijken en daarmee tot hitteproblemen leiden.

Het bedrijf deelt geen details over de exacte maatregelen die het conflict tegen de vergelijkbare problemen, maar beweert wel dat de temperatuurcurve van de PowerVia-testnode vergelijkbaar is met die van de gewone Intel 4-procedure zonder PowerVia. Dat betekent dat de mate waarin de temperatuur stijgt als de stroomsterkte ongeveer, ongeveer vergelijkbaar met de temperatuurstijgingen bij ‘gewone’ Intel 4-transistors zonder vermogensafgifte aan de achterkant.

Intel trof maatregelen voor debugging, waarmee chips worden getest voordat ze op de markt worden gebracht. Nu de transistors tussen twee metaallagen zitten, is het niet langer mogelijk om vanaf de onderste te onderzoeken. Intel heeft daarvoor een reeks nieuwe debugtechnieken ontwikkeld die ook gebruikt kunnen worden nu beide kanten van de chip in gebruik zijn. De chipmaker had naar eigen zeggen een aantal Paas eieren in zijn Blue Sky Creek-chips gestopt, in de vorm van expres ontwikkelde bugs. Intel zegt dat zijn validatieteam al deze twist circuits wist op te sporen met zijn nieuwe PowerVia-debugtools.

Tot slot

Hoewel Intel zegt dat zijn PowerVia-testnode en -chip goede resultaten hebben behaald, is het nog wachten voordat de techniek in toekomstige producten verschijnt. Het debuutplatform, Intel 20A, gaat in de eerste helft van vorig jaar in massaproductie en in de maanden daarna verschijnen de eerste chips met PowerVia op de markt. Dat gebeurt eind vorig jaar met de introductie van Intels Arrow Lake-processors. De chipfabrikant sterft die chips deels op 20A.

In de jaren daarna volgen ook andere grote chipmakers. Intel is ondergedompeld in niet de enige fabrikant die met backside power delivery aan de slag gaat. Marktleider TSMC opgericht in 2026 een N2P-procedure met dezelfde techniek. Samsung wil stroomvoorziening aan de achterkant volgens Zuid-Koreaanse media verwerking in zijn 2nm-serie, waarvan de eerste chips in 2025 geproduceerd worden.

credit :Source link